2. Alat dan Bahan

[Kembali]

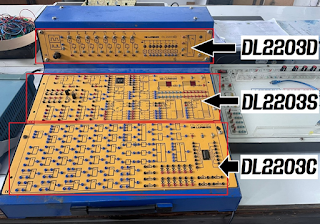

- Modul D'Lorenzo ( Panel DL 2203C, Panel DL 2203D, Panel DL 2203S)

Pada percobaan 2 modul 2 yaitu menggunakan T flipflop, T flip flop berasal dari J-K flip Flop yang input J dan K nya dijadikan 1. Disini inputan berupa switch SPDT dan output menggunakan LED. Switch SPDT terhubung pada power dan juga ground, dimana kaki yang terhubung pada power mengindikasikan logika 1 dan yang terhubung pada ground mengindikasikan logika 0. Untuk keadaan input divariasikan dan diamati outputnya untuk masing-masing flipflop.

T flipflop disini memiliki kaki input Set (S) dan Reset (R) yang keduanya berkondisikan active low. Sehingga jika salah satu kaki S atau R dalam kondisi on. Maka output pada kaki Q dan Q' akan dipaksakan bernilai sesuai dengan kaki input yang aktif. Dimana jika kaki S aktif, maka output kaki Q = 1 dan Q' = 0. Sedangkan jika kaki R aktif, maka output kaki Q = 0 dan Q' = 1. Jika kedua kaki S dan R aktif secara bersamaan, maka akan terjadi efek saling meniadakan. Dimana kedua input akan melakukan set dan mereset secara bersamaan. Sehingga output dari kaki Q dan Q' beernilai 1 1.

Berikutnya jika kaki S dan R tidak aktif atau diberkan input logika 1. Maka kedua flipflop bekerja dengan prinsip inputnya sebagai berikut:

Pada T flipflop terdapat 2 kaki input selain S dan R yaitu T (J-K) dan CLK. Dimana CLK akan menjadi penentu perubahan output terhadap input T yang diberikan. Disini CLK berkondisi active low, sehingga setelah 1 periode dan pulsa bertukar low, output akan bertukar sesuai dengan input T. Input pada kaki T adalah 0, maka output tidak akan berubah dari kondisi sebelumnya. Namun jika input pada T adalah 1 maka output pada kaki Q dan Q' akan berada dalam keadaan Toggle.

1. Analisalah hasil yang didapat pada percobaan 2, dengan keempat kondisi yang ada pada jurnal! Bagaimana Output yang dihasillkan dan jelaskan kenapa output bisa seperti itu!

Pada percobaan 2, dilakukan 4 kali percobaan dengan memvariasikan inputan pada T flip flop.

Kondisi 1. T bersifat X, preset 1, dan clear 0. Pada T flip flop sifat preset hampir sama dengan set yaitu menjadikan output 1. Dan clear hampir sam dengan reset yaitu menjadikan output 0. Pada kondisi ini, karena reset dan set sama sama aktif low, dan reset bernilai 0 sehingga output yang dihasilkan ialah 0.

Kondisi 2. Merupakan kebalikan dari kondisi 1. Yaitu T = don't care, Reset 1, dan set =0. Sehingga output yang dihasilkan akan bernilai 1. Karena Set aktif sebab diberi inputan 0.

Kondisi 3. pada kondisi ini, T dijadikan X, R dan S diberi nilai 0. Output yang dihasilkan ialah 1 (Q) dan 1 (Q') hasil output yg sama sedangkan seharusnya Q dan Q' berlawanan ialah disebabkan karena kedua pin R dan S sama sama aktif. Sehingga terjadi kondisi tersebut.

Kondisi 4. T diberi clock, dan R dan S diberi 1 sehingga R dan S tidak aktif. Jadi Output yang dihasilkan ialah bersifat toggle setiap clock aktif.

2. Pada percobaan 2 tentang T flip flop, digunakan IC 74LS112. Jelaskan jenis-jenis dan fungsi dari masing-masing kaki(pin) pada IC tersebut!

Pada percobaan 2 yaitu T flip flop dengan menggunakan IC 74LS112. Pada IC 74LS112 ini terdapat inputan pin J dan K. Yang mana kedua inputan ini sama sama dihubungkan ke vcc sebagai inputan T. Tujuan keduanya dihubungkan ke VCC ialah karena sesuai dengan pengertian T flip flop yang berasal dari JK flip flop yang kedua kakinya dijadikan 1. Selanjutnya terdapat pin R yang aktif low. Dimana pin reset ini akan mensetting output menjadi 0 saat ia aktif yaitu bernilai low atau 0. Pin S yang juga aktif low akan mensetting output menjadi 1 ketika pin S diberi nilai 0. Dan terakhir terdapat Pin CLK (Clock). Pin ini pada IC 74LS112 memiliki fungsi untuk memberikan sinyal clock yang mengatur perubahan keadaan (flip) pada kedua flip-flop JK di dalam IC tersebut. Sinyal clock digunakan untuk mengsinkronkan operasi flip-flop, sehingga perubahan input pada saat sinyal clock aktif akan terjadi pada output flip-flop setelah perubahan clock

Tidak ada komentar:

Posting Komentar