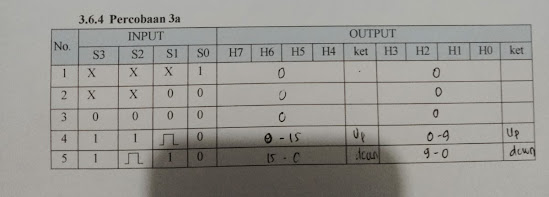

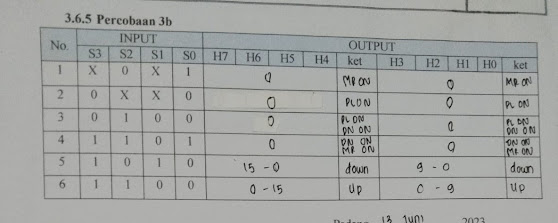

Pada percobaan ini terdapat 2 buah IC yaitu IC 74192, decoder 74LS47, seven segment Anoda, gerbang OR, gerbang NOR, dan 6 buah SPDT. Selanjutnya Pada IC 74192 terdapat 4 buah input yaitu D0-D3 dan 4 buat output yaitu Q0-Q3. Dimana input D0-D3 nya masing-masing mendapatkan input dari SPDT. selain itu juga terdapat pin Up, pin DN, PL dan MR. PL (paralel load) aktif low dan diberi logika 1 sehingga tidak aktif, dan MR (Master reset) aktif high diberi logika 0 sehingga MR juga tidak aktif. Pin DN mendapat input dari gerbang NOR yang salah satu kaki inputannya berasal dari hasil feedback output IC tersebut.

Selanjutnya pada IC 74LS47 terdapat 4 buat input yaitu A-D dan 7 buah output yaitu Q0-Q7 yang dihubungkan dengan sevent segment common anoda. Masing-masing input IC 74LS47 berasal dari output IC 74192. lalu pada IC ini untuk BI,RBI dan LT yang aktif low dan diberi inputan 1 sehingga ketiga inputan ini tidak digunakan atau tidak aktif,

Kemudian saat rangkaian disimulasikan (dijalankan) terlihat pada seven segmen anoda menunjukkan angka 9. dimana hal tersebut terjadi pada saat di IC 74192 outputnya yang diumpang balikkan kepada gerbang OR dan output dari gerbang OR akan masuk ke salah satu dari kaki input gerbang NOR. dan pada gerbang NOR diberi CLK, umpan balik terjadi dikarenakan PL nya aktif.

Lalu pada decordernya terdapat BI dimana ia dapat menghidupkan/mematikan seven segmen, sedaangkan pin LT ia berfungsi untuk melihat apakah lampu aktif atau tidak.