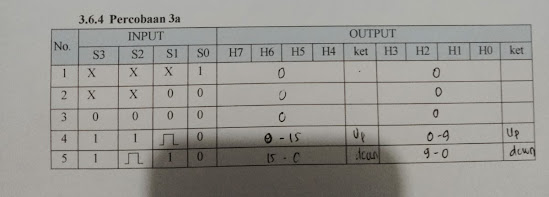

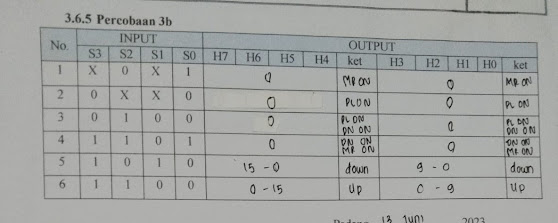

Berdasarkan percobaan, digunakan 2 IC yaitu 74193 dan 74192. Keduanya memiliki beberapa pin yaitu :

· Pin UP : sumber S1 : counter up

· Pin Down : sumber S2 : counter down

· Pin reset : sumber S0 dan S1 : jika keduanya 1 maka counter off

· Pin D0,D1,D2,D3 sebagai input.

Pada percobaan, pin D0 terhubung ke Q0, D1 ke Q1, D2 ke Q2, dan D3 ke Q3.

Untuk mengatue counter menjadi up besar maka pin UP diberi masukan clock dan pin DN diberi logika 1. Jika perhitungan dari besar ke kecil maka dilakukan sebaliknya. Pin PL yang merupakan paralel load yang jika PL aktif maka output akan menghasilkan perhitungan otomatis dan jika PL tidak aktif maka output akan diatur oleh pin D0, D1, D2, dan D3 (keluaran akan diatur secara manual).Pin MR yang merupakan master reset.

Tidak ada komentar:

Posting Komentar