2. Alat dan Bahan

[Kembali]

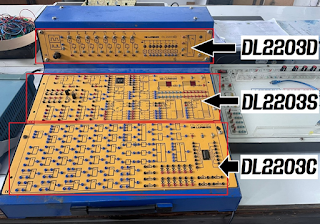

- Modul D'Lorenzo ( Panel DL 2203C, Panel DL 2203D, Panel DL 2203S)

prinsip kerja rangkaian Multivibrator asingkronus di atas menggunakan 4 buah jk flipflop yang yang jk nya telah terhubung dengan power. Sebagaimana di ketahui jika multivibrator asinkronus maka untuk 1 inputan clock hanya mempengaruhi flip flop pertama saja , sedangkan flip flop kedua , ketiga , dan seterusnya untuk inputan clocknya berasal dari output Q pada flip flop sebelumnya ( jika ingin membuat kondisi Counter Up ) dan Q' ( Jika ingin membuat kondisi Conter Down ). Karena J dan K terhubung ke power maka ia akan selalu bernilai 1, sehingga input pada jk flipflopnya bersifat toggle sesaui dengan ketentuan Tabel kebenaran, maka Output toogle pada masing-masing IC akan berubah sesuai aktif pada clock yaitu aktif low atau fall time ( dilihat dari rangkaian IC nya terdapat gerbang inverter pada Clock, maka dari itu ia Fall Time.

pada percobaan pertama clock inputnya hanya terdapat pada jk flipflop pertama atau pada paling kanan saja sehingga saat clock yang mula mula dari 0 menuju rise time. maka output jk flipflop yang pertama tidak ada perubahan begitu juga pada jk stereusnya.

kemudian saat clock tersebut dalam keadaan fall time maka jk flipflop pertama akan berubah menjadi 1. namun jk flipflop kedua tidak berpengaruh karena jk flipflop kedua bergantung pada output di jk flipflop pertama sehingga terjadi delay time. sehinnga clock ic kedua dalam keadaan rise time sehingga output ic kedua berlogika 0 begitun seterusnya sampai ic ketiga dan keempat mendapat kenaikan atau penurunan dari flipflop. Jika Di amati Timing diagramnya maka untuk Output dari Flip flop pertama akan membentuk pola ( 0101010101010101), lalu unttuk output pada flip flop 2 karena ia clocknya menyesuaikan dengan output Q sebelumnya maka pola untuk flip flop ke dua ialah (0011001100110011), begitu juga dengan flip flop ke tiga dengan pola ( 0000111100001111) dan terakhir karna pada rangkaian hanya memakai 4 flip flop maka untuk inputan clock pada flip flop ke empat ini berasal dari output Q pada Flip Flop ketiga sehingga nantinya akan memebentuk pola berikut jika Counter Up ( 0000000011111111). Pola tersebut benar adanya setelah di buktikan dengan menganalisa rangkaian dalamnya lalu mengilustrasikannya di timing diagram.

5. Video Rangkaian [Kembali]

1. Analisa output percobaan berdasarkan ic yang digunakan?

IC yang digunakan pada percobaan 1 yaitu flipflop jenis T. Dimana clock dihubungkan ke H, output T flip flop 1dihubungkan ke clock T flip-flop 2 yang diparalelkan dengan H0, output T flip flop 2 dihubungkan ke clock T flip-flop 3 yang diparalelkan dengan H1, output T flip flop 3 dihubungkan ke clock T flip-flop 4 yang diparalelkan dengan H2, dan output dari T flip flop 4 dihubungkan ke H3.

H(Clock) fall time hal ini karena ketika lampu indikator H mati maka terjadi perubahan output ( H0, H1, H2, H3). Ketika module D Lorenzo telah dihubungkan ke power supply, maka output yang diperoleh untuk

H0 = 0 1 0 1 0 1 0 1 0 dst,

H1 = 0 0 1 1 0 0 1 1 0 dst,

H2 = 0 0 0 0 1 1 1 1 1dst,

H3 = 0 0 0 0 0 0 1 1 1 dst

Dan dari perolehan output tersebut dapat diketahui bahwa counter pada percobaan ini merupakan penghitung maju atau up counter. Dan dari hasil output yang diperoleh dapat diketahui bahwa ketika output flip flop sebelumnya terjadi perubahan dari 1 ke 0. Maka untuk output flip flop setelahnya akan bersifat toogle sehingga berlawanan dengan output flip flop tersebut sebelumnya. Sedangkan ketika output flip flop tersebutnya 00, 01, atau 11. Maka untuk output flip flop berikutnya tidak berubah atau sama seperti output sebelumnya.

2. Analisa sinyal output yang dikeluarkan jk flipflop kedua dan ketiga?

Output yang dihasilkan dari JK flip flop kedua dan ketiga jika diamati jumlah bitnya yaitu kelipatan dua dari output sebelumnya. Sehingga ketika output H0( flip flop pertama) = 0 1 0 1 0 1 0 1, maka H1 (flip flop kedua) = 0 0 1 1 0 0 1 1 dan H2 ( flip flop ketiga) = 0 0 0 0 1 1 1 1.

Sehingga dari output yang dihasilkan bentuk timming diagram seperti pada jurnal dengan kondisi fall time yang mana bit yang sama akan semakin banyak di flip flop terjauh dari clock. Dan semakin dekat flip flop ke clock, maka perubahan output dari 0-1 atau 1-0 semakin cepat

7. Link Download

[Kembali]

Tidak ada komentar:

Posting Komentar